Краткое описание протокола FXP

FXP - это программно-аппаратное решение, предназначенное для систем, построенных на основе микросхем FPGA.

Оно представляет собой протокол связи с компьютером, решающий следующие основные задачи:

- поддержка модульной организации устройства (кросс-плата, доп. ячейки);

- независимая конфигурационная загрузка микросхем FPGA в составе устройства;

- высокоскоростная передача данных между любой мс. FPGA в устройстве и компьютером;

- поддержка потоковых режимов передачи (потоков в реальном масштабе времени);

Протокол условно разбит на три уровня: физический, логический и программный.

Физический определяет архитектуру и среду передачи на уровне ячеек (доп. плат расширения),

межплатных соединений и соединения с компьютером. Логический уровень определяет типы и

строение пакетов передачи, а также алгоритмы их обработки.

Программный представляет интерфейс с драйвером и пользовательской библиотекой.

Предложенная реализация протокола обладает следующими характеристиками:

- внешний интерфейс связи с компьютером - USB1.1/2.0;

- до семи географически адресуемых ячеек (плат) в устройстве;

- до 16 адресуемых микросхем FPGA на каждой ячейке;

- независимая конфигурационная загрузка любой мс. FPGA Xilinx® серии Virtex®/E/II/, Spartan®II/IIE/III, размещенной на любой ячейке устройства;

- чтение/запись в любую микросхему FPGA в устройстве со скоростью до 60МБ/с.;

- поддержка потоковых режимов передачи;

- программный интерфейс с аппаратной частью системы, поддержка платформ Windows® NT5 (2K/XP/Server 2003), Windows® 98/ME;

- автоматическое программное определение устройства и его конфигурации, PnP;

- реакция на сигнал аппаратного прерывания в виде вызова обработчика;

Физический уровень

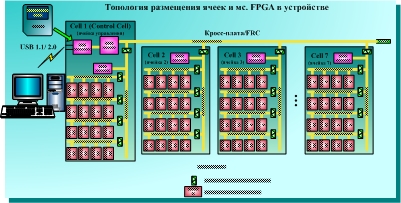

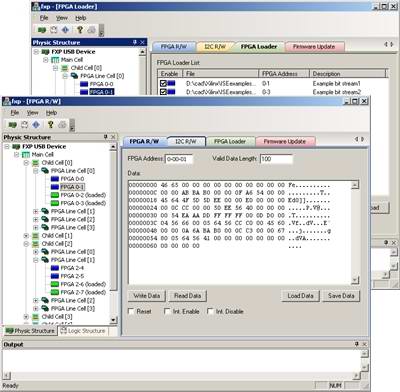

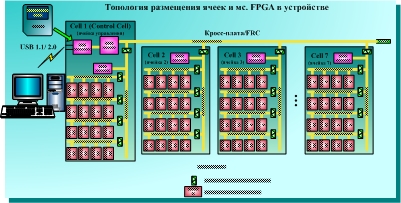

На рис.1 изображена поддерживаемая протоколом топология размещения мс. FPGA в устройстве.

Рисунок 1

Протокол поддерживает два режима работы:

- автономный, когда последовательность команд инициализации считывается с FLASH-карты;

- взаимодействие с компьютером;

Во втором случае на уровне драйвера операционной системы формируются пакеты,

которые включают в себя адрес ячейки, адрес FPGA, служебную информацию и данные.

Далее они отправляются через USB к микроконтроллеру FX2.

Разбор пакетов производится в мс. DCU (Data Control Unit),

данные затем появляются на мультиплексированной шине адреса/данных.

Для обеспечения контроля над волновыми характеристиками линий,

уменьшения емкостной нагрузки шина данных и линии управления разбиты на

сегменты A, B и C (необходимость такого решения показана путем моделирования).

Дешифрация адреса ячейки и целевой FPGA, а также коммутация сегментов производится в мс. PBM (Process Bus MUX).

Интерфейс с целевыми FPGA. Адресация

Интерфейс с целевыми FPGA состоит из линий, указанных в следующей таблице

|

Название1

|

Направление, I/O

|

Назначение

|

|

Передача данных:

|

|

DATA[15:0]

|

I/O

|

шина адреса/данных

|

|

nPAEN

|

I

|

строб адреса

|

|

nWREN

|

I

|

строб чтения

|

|

nRDEN

|

I

|

строб записи

|

|

PFULL

|

O

|

подтверждение записи (для потоковых режимов - флаг переполнения FIFO)

|

|

PEMPTY

|

O

|

подтверждение чтения (для потоковых режимов - флаг опустошения FIFO)

|

|

nCE

|

I

|

выбор микросхемы (Chip Enable)

|

|

nRESET*

|

I

|

инициализация процесса

|

|

PERROR*

|

O

|

сигнал ошибки (для потоковых режимов - потеря слова в FIFO)

|

|

CLK

|

I

|

сигнал синхронизации

|

|

Запрос прерывания:

|

|

nINT

|

O

|

запрос прерывания

|

|

Линии конфигурационной загрузки (режим SelectMap)2:

|

|

nCS

|

I

|

выбор микросхемы (в режиме конфигурации)

|

|

nPROGRAM

|

I

|

сброс конфигурационной загрузки

|

|

RNW*

|

I

|

строб чтения/записи

|

|

DONE*

|

O

|

завершение процесса конфигурации

|

|

nINIT*

|

O

|

инициализация конфигурационной памяти

|

|

CCLK

|

I

|

сигнал синхронизации (в режиме конфигурации)

|

- Линии отмеченные (*) являются опциональными.

- Для конфигурационной загрузки также используется DATA[7:0]

|

Назначение стробов аналогично их назначению в буфере FIFO.

Таким образом, с точки зрения внешнего интерфейса,

целевая микросхема FPGA представляет собой набор адресуемых FIFO-буферов.

Внутри же микросхемы эти адресуемые блоки могут выполнять любые задачи,

в том числе отличные от FIFO, т.к. их внутренний интерфейс ничем не ограничен.

Такие блоки, каждому из которых соответствует свой адрес,

получили название "процессы". Полный адрес процесса состоит из следующих полей:

- адрес ячейки (3 бита);

- адрес целевой микросхемы FPGA (5 бит);

- адрес процесса внутри FPGA (8 бит);

Адрес ячейки и целевого FPGA дешифрируется в мс. PBM,

в соответствии с этим адресом выставляется сигнал nCS, предназначенный адресуемой микросхеме.

Адрес процесса дешифрируется внутри целевой микросхемы.

Все, что требуется разработчику для реализации физического

уровня протоколы в своем устройстве, скопировать схему, приведенную в документации на протокол,

и подсоединить выводы целевых FPGA к соответствующим линиям протокольной части.

Логический уровень

Типы и назначение пакетов относятся к внутренней структуре протокола,

их подробное описание и алгоритмы их обработки приведены в документации на DCU и PBM.

Автоконфигурация

Протокол предусматривает автоматическое определение устройства и его конфигурации.

Для этого на каждой ячейке предусмотрена микросхема EEPROM,

в памяти которой содержится вся необходимая информация о данной ячейке

(количество целевых FPGA, их адреса и т.д.).

Кроме того, часть ее объема отводится для хранения произвольной пользовательской информации.

Программный уровень

Программный уровень представлен пакетом программного обеспечения, в который входят:

- драйвер и описание его интерфейса;

- набор пользовательских библиотек;

- программа FXP MANAGER и описание интерфейса подключения к ней пользовательских программных модулей;

Приложение FXP MANAGER предназначено для двух основных задач:

- отладка системы, т.е. реализация низкоуровневых операций протокола, поддерживается скрипт на основе языка TCL с расширенным набором команд, что позволяет автоматизировать и упростить отладку.

- интеграция пользовательских программных модулей, предназначенных для работы с конкретным устройством;

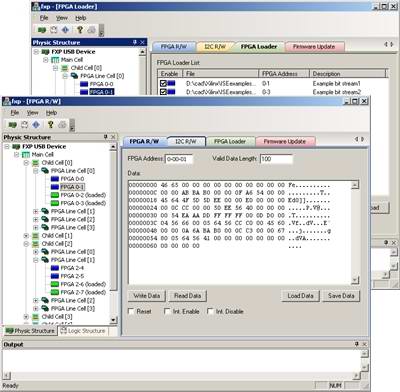

Внешний вид пользовательского интерфейса показан на рис.2.

Рисунок 2

Заключение

Протокол FXP изначально рассчитан на применение в больших системах,

состоящих из нескольких ячеек и большого количества микросхем FPGA,

где его преимущества проявляются в полной мере.

Для недорогих же решений предложена его модификация под названием FXPL (FXP Lite).

Изменения внесены только в физический уровень.

Логического и программного уровней изменения не коснулись,

поэтому с программной точки зрения протокол FXPL предоставляет полный набор возможностей FXP.

Рекомендации по применению

Поскольку внешние интерфейсы протокола полностью документированы,

то нет нужды разбираться во внутренней структуре протокола.

Для практического применения достаточно скопировать Reference Design из

соответствующей документации, скачать драйверы,

прошивку микроконтроллера и битовые загрузки DCU и PBM.

В таком случае мы настоятельно рекомендуем приобрести FXPCTL Evaluation Board,

что поможет Вам при отладке Ваших устройств и при ознакомлении с протоколом.

Желаем успеха!

Коллектив разработчиков AdvanteX

|